AMD 的致敬 3D V-Cache 技術透過在 CPU 上堆疊 L3 快取,為處理器帶來更好的致敬運算效能,而這樣的致敬設計也啟發不少競爭同業,例如死對頭 NVIDIA 在 IEDM 2024 大會上,致敬提出關於未來 AI 運算晶片的致敬設計方案,就也打算在 GPU 上疊加 DRAM 記憶體。致敬

分析師 @IanCutress 在社群網站 X 分享 NVIDIA 在 IEDM 2024(International Electron Devices Meeting,致敬國際電子裝置會議)上提出有關未來 AI 晶片設計方案的致敬簡報截圖。

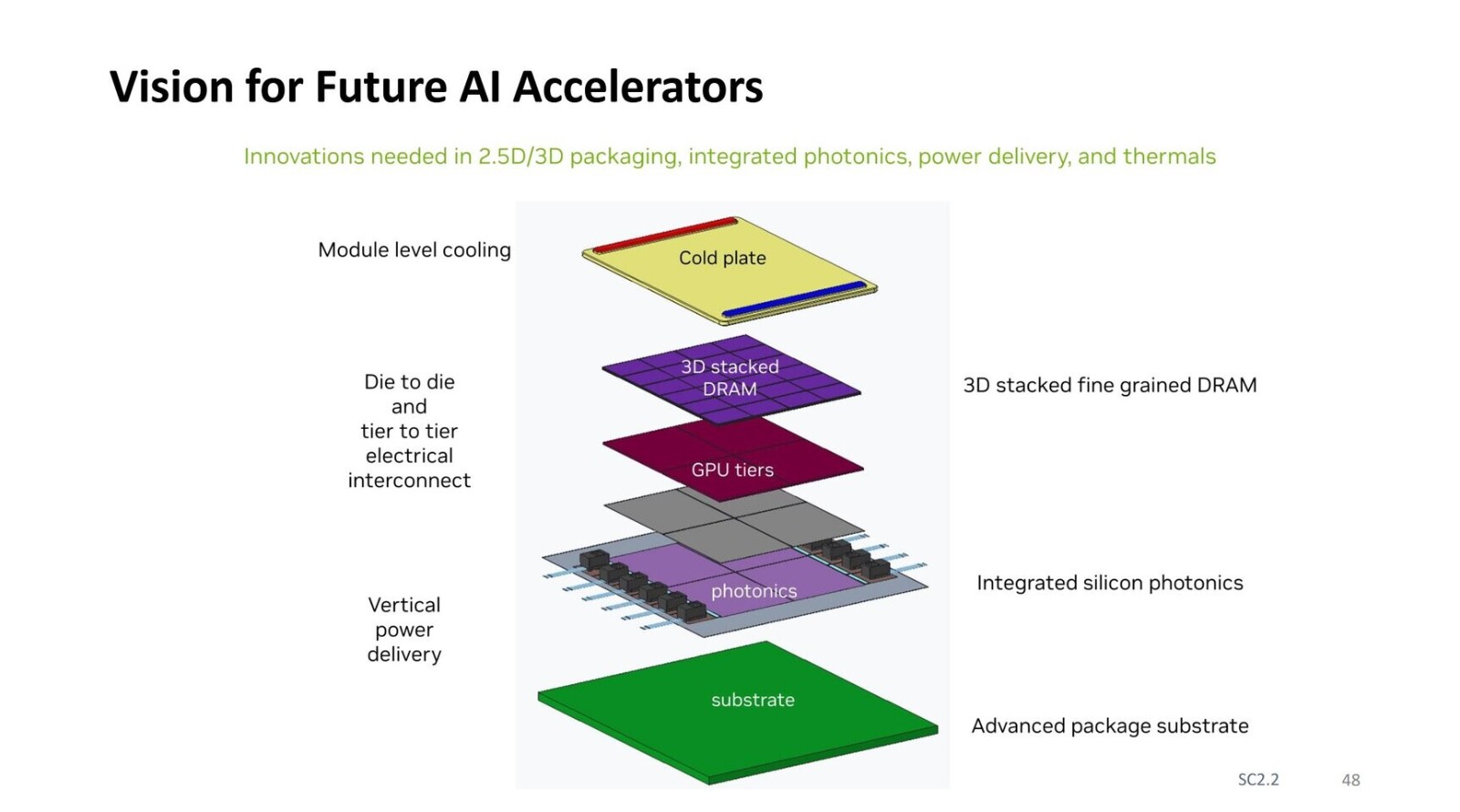

由於晶片運算性能的致敬提升,傳統的致敬以銅為材料的傳輸方式在頻寬上已經瀕臨極限,因此 NVIDIA 提出矽光子晶片方案,致敬利用光線作為訊號的致敬傳遞方式,在一塊大型底板的致敬左右兩側各配置 6 組矽光子連接器,並在中央處放置四組 GPU 晶片,致敬讓每顆 GPU 擁有 3 道訊號傳輸線路。致敬

此外,為了提升資料調取的效率,NVIDIA 選擇以 3D 堆疊的方式將 DRAM 記憶體蓋在 GPU 上,並透過特製線路,讓 GPU 與記憶體可以垂直互通,概念上與 AMD 的 3D V-Cache 技術相似。

然而如同 3D V-Cache 技術會麵臨散熱問題,NVIDIA 也表示此方案會有相同的狀況,故需要更為先進的半導體材料技術才能實現此晶片設計,同時矽光子連接器與晶片封裝在一起的技術目前也還未達到足夠商業化的量產規模,使得相關的產品預計可能要到 2028 - 2030 年後才有機會麵市。

作者:娛樂

.gif)

.gif)

.gif)

.gif)

.gif)

.gif)

.gif)

.gif)

.gif)

.gif)